Become a leader in the IoT community!

Join our community of embedded and IoT practitioners to contribute experience, learn new skills and collaborate with other developers with complementary skillsets.

Join our community of embedded and IoT practitioners to contribute experience, learn new skills and collaborate with other developers with complementary skillsets.

Can anyone tell me how do you decide or calculate the stack size for the task(thread) when you do xTaskCreate() in freeRTOS.?

Having this issue!!

20250217_214618.mp4

This requires understanding of exact memory resources of an mcu. Then depending on what intended task is doing and how much memory it requires to perform its operation you gauge some number and assign stack size. Later on it’s a good practice to use advance debugger to know real time requirement of stack size so you can add or remove unused allocated space.

And my program is working with stack size of 2024 but not with 1024 and in the tutorial his programing is working with 1024 stack size

its possible perhaps in tutorial different microcontroller been used from the same vendor. I mean it depends

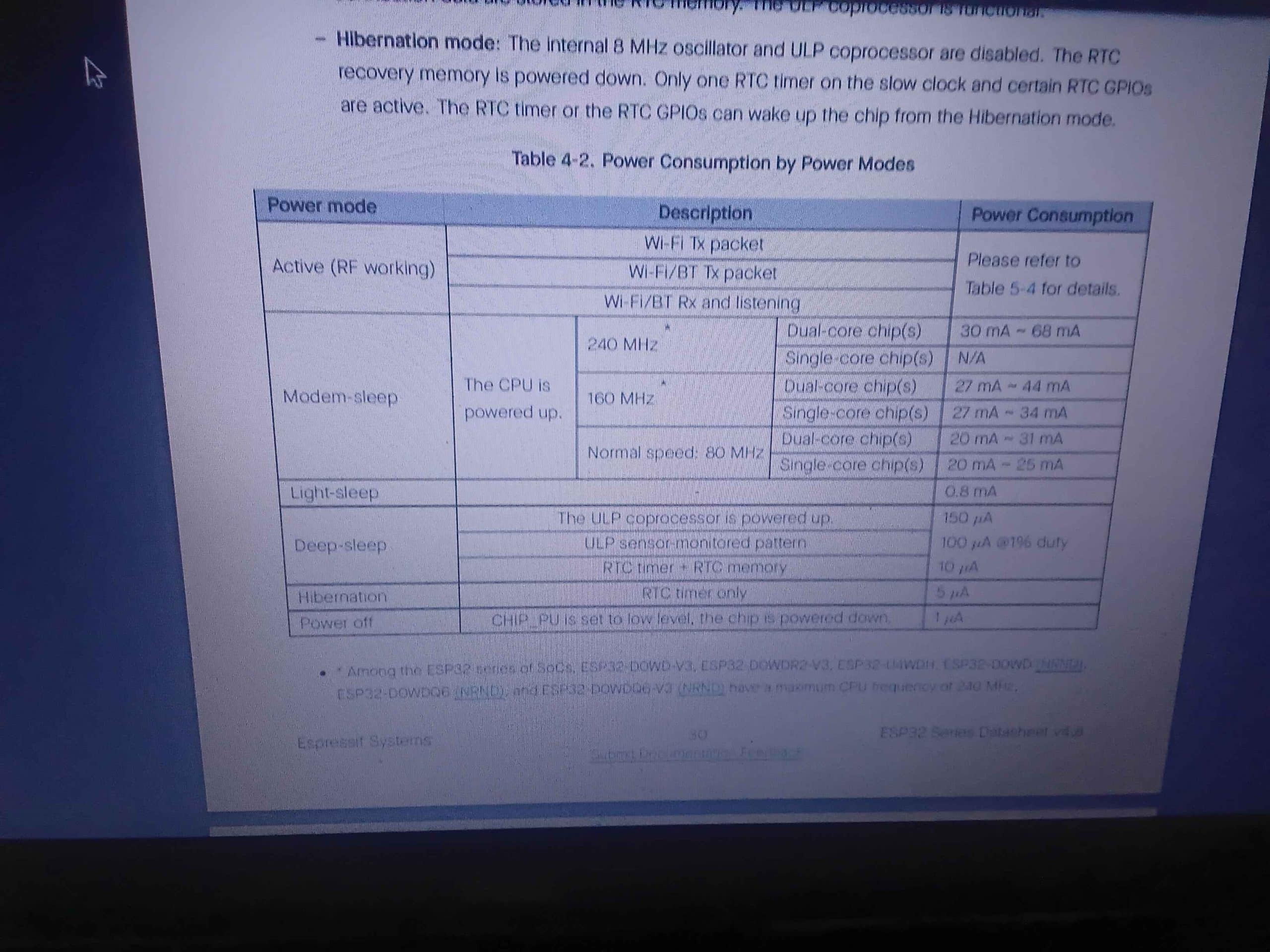

It is for esp32 c3 and i have esp32

Hope you know here ur dealing with 2 different architecture. esp32-c3 is RISC V and generic esp32 uses xtensa LX. So this difference is obvious

Oh i haven’t notice this

But still i check esp32 have more ram and stack size than c3 still i have to give 2024 in my esp32

and 1024 in c3

this could be why RISC V-based mcu is preferred over xtensa. Maybe be it has to do with its internal memory structure.

Damm… do i have to study architect to understand this?

depends but just knowing memory size and layout is mandatory

the problem of esp is they use various architecture. arm, xtensa, risc-v

but you can determine guess how much to give depending on how many variables, arrays you are using in your code also even if you are using data type like uint8_t there is a good chance thats taking 32bit in memory

because cpu can access a word of memory in a cycle efficiently thats important to keep the performance

It was just a hello world task print value int 1 passed through the pointer

And now i can see the practical difference with the rics-v and xtensa 🙂, rics architecture really have reduced instruction ig thats why they are taking less stack memory than xtensa

that could be the case. dont have much idea on risc or xtensa

Me to, but i have seen some ricsv assembly instruction there are very big not like 8051 assembly instruction, but they are able to much thing in less instruction as compared to older assembly instruction.

Esp32 have efuse

Damm this is cool

CONTRIBUTE TO THIS THREAD